Specific configuration for the M670 target ECU.

None (Main library). (See Section 2.3, “Licensed Features”.)

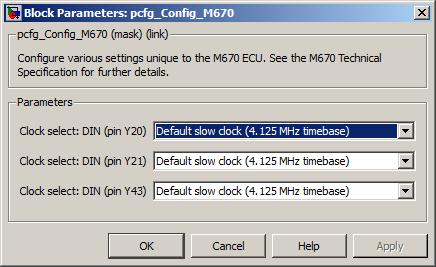

The pcfg_Config_M670 block configures pins Y20, Y21, and Y43 to set the resolution of those frequency inputs.

If the block is not present in a model, then the platform software configures the pins to the default slow clock setting.

For MIOS-controlled digital I/O, multiple clock speeds can be chosen:

Slow clock: 4.125Mhz timebase.

Medium Clock: 8.25Mhz timebase. For inputs 0.75 Hz to 2500 Hz with a minimum resolution of at least 0.5 Hz

Fast Clock: 16.5Mhz timebase. For inputs 1.6 kHz to 60 kHz with a minimum resolution of at least 218 Hz.